# Électronique

- J. Pouxe, R. Foglio, C. Barruel, J.-L. Bouly, G. Bosson, P. Cavalli, D. Bouteloup, D. Dzahini, L. Eraud, L. Gallin Martel, J.-P. Girard, J. Larruat, E. Lagorio, J. Mirasolo, S. Muggeo, A. Patti, J.-P. Richer, O. Rossetto, J.-P. Scordilis, D. Tourres, C. Vescovi, Y. Vedrene, M. Yamouni

- A team of electronics engineers and technicians develops ASICs for high density electronics which meet the requirements of high energy physics (ATLAS) and astrophysics (AMS, Planck, EUSO)

# DÉlectronique spécifique à certaines expériences

#### **AMS**

La campagne de test en cosmiques du prototype d'imageur Cherenkov s'est déroulée durant le premier semestre 2002. Ce prototype, construit en collaboration avec le CIEMAT de Madrid, est constitué de 96 photomultiplicateurs 16 anodes ce qui représente environ un septième du détecteur final. Durant l'été 2002 le prototype a été préparé en prévision des tests sous faisceau qui se sont déroulés en octobre au CERN. Ces tests ont permis de valider le fonctionnement de l'électronique de lecture des photomultiplicateurs. Le LPSC est alors entré dans la phase de production des 680 modules du détecteur final. Le circuit intégré 16 voies assurant la conversion charge tension des signaux d'anodes des photomultiplicateurs a été produit à 1 400 exemplaires. Un banc de test spécifique a permis le contrôle des circuits, le rendement obtenu de 80 % est satisfaisant et conforme aux prévisions. Cette phase comprend aussi la fabrication et le câblage des circuits imprimés ainsi que le montage des photomultiplicateurs sur ces derniers. Une coque en plastique est alors glissée autour du photomultiplicateur et du circuit imprimé contenant le diviseur haute tension et finalement du silicone est injecté dans la coque, assurant à la fois le maintien mécanique et l'isolation électrique (potting). Un nouveau banc de test permettant la calibration simultanée de 16 modules a également été développé au cours de l'année 2003. Le prototype d'imageur a été équipé de 96 modules de dernière génération et a été à nouveau testé en faisceau au CERN en octobre 2003.

La prochaine étape est le test des 680 ensembles photomultiplicateurs et modules d'électronique avant la livraison au laboratoire CIEMAT de MADRID.

#### **Planck**

Dans le cadre du projet Planck, le service électronique du LPSC est impliqué dans la conception de deux électroniques de contrôle de machines cryogéniques. Le Sorption Cooler développé par le Jet Propulsion Laboratory (NASA - USA) permet la descente en froid de 50 K à 20 K tandis que le Dilution Cooler développé par le CRTBT et construit par Air Liquide permet d'atteindre les 0,1 K.

# **Sorption Cooler Electronics**

L'électronique du Sorption Cooler développé conjointement par le service d'acquisition de données et le service d'électronique est divisée en trois cartes dont deux sont sous la responsabilité du service d'électronique :

- la carte de puissance se charge de l'alimentation électrique de l'électronique par l'intermédiaire d'un convertisseur DC/DC et assure le contrôle de la puissance fournie au refroidisseur. Les résistances chauffantes des compresseurs à absorption doivent notamment être alimentées séquentiellement de manière à dissiper une puissance qui peut varier de quelques dizaines de Watts à 250 W. D'autres résistances chauffantes sont également commandées entre autres pour des circuits de débouchage et un circuit de régulation des fluctuations de température.

- la carte d'acquisition assure la lecture de 30 capteurs de température avec des précisions pouvant atteindre 5 mK, de 8 capteurs de pression et d'une vingtaine de capteurs internes (températures de l'électronique, tensions, courants).

Deux prototypes de cette électronique ont été fabriqués et testés sur simulateur au LPSC durant le premier semestre 2002. En septembre 2002, un de ces prototypes a été couplé au Sorption Cooler au JPL après une nouvelle validation sur le simulateur du JPL. Ces premiers tests ont été un succès et ont permis de faire fonctionner correctement le cryogénérateur, malgré l'absence de certaines fonctions non encore implémentées. Une dernière campagne de tests du prototype a donc été effectuée début mai 2003, de sorte que ces nouvelles fonctionnalités ont été validées.

Fin avril 2003, après un appel d'offre de l'ESA, la société ASTRIUM/CRISA (Espagne) a été choisie pour la fabrication des modèles de qualification et des modèles de vol de cette électronique. Il s'en est suivi une longue période d'échanges entre le LPSC et ASTRIUM/CRISA afin d'améliorer le design de l'électronique et de le rendre plus compatible avec les exigences du spatial. Un design définitif a été présenté par CRISA fin novembre 2003.

#### **Dilution Cooler Electronics**

L'électronique du cryogénérateur à dilution d'He³/He⁴ est aussi développée conjointement par les services d'électronique et d'acquisition de données. Contrairement à l'électronique du Sorption Cooler, dont la fabrication a été confiée à Astrium, le LPSC est chargé, en plus de l'étude du prototype, du développement et de la fabrication des modèles de qualification et de vol. Les principales fonctions de cette électronique sont :

- l'alimentation électrique grâce à un convertisseur DC/DC ;

- la communication avec le calculateur de l'instrument HFI;

- la commande de 12 vannes bistables contrôlant les circuits d'alimentation en He<sup>3</sup> et He<sup>4</sup>;

- la commande de 8 résistances chauffantes pour des circuits de débouchage et l'activation d'un switch thermique;

- la lecture de 6 capteurs de pression et 14 sondes de température.

Un premier prototype a été développé fin 2003 et doit subir des tests fonctionnels afin d'en valider le design.

Un modèle de qualification sera ensuite fabriqué sous la responsabilité du LPSC, pour être intégré sur la « boîte à vannes » d'Air Liquide fin avril 2004. Les tests de qualification en cycle thermique doivent être réalisés avant intégration alors que les tests de vibrations et de compatibilité électromagnétique seront faits sur le système intégré en Mai et Juin 2004.

Suivra ensuite la fabrication, le test et l'intégration des deux modèles de vol fin 2004 - début 2005.

# Électronique Analogique Frontale pour l'expérience EUSO

Pendant la phase A, le Service Électronique a en charge le développement d'un ASIC analogique (Analog Front-End Electronics) pour évaluer les performances de différentes architectures pour traiter les signaux provenant des 5 000 Photomultiplicateurs munis de 36 anodes. Trois prototypes ont déjà été réalisés en technologie Austriamicrosystems 0,35 µm CMOS pour les deux premiers et BiCMOS-SiGe pour le dernier.

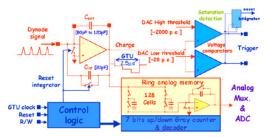

Figure 1 : Voie dynode.

La **voie dynode** (Figure 1) est constituée d'un préamplificateur de charge dont le condensateur (100 pF externe) est vidé par un interrupteur analogique à la fin de chaque cycle GTU (Gate Time Unit ~ 2,5  $\mu$ s) après stockage de la charge dans une mémoire analogique de 128 cellules. Ce préamplificateur est associé à deux comparateurs (signaux pour le trigger) et à un système de détection de saturation du signal intégré.

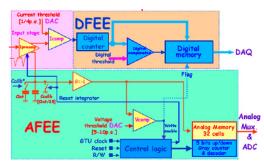

Chaque voie anode (Figure 2) est constituée d'un préamplificateur de courant « cascodé », possédant deux sorties en courant, associé à un amplificateur « auto-zéro » compensant le courant de fuite. La première sortie fournit le signal pour le comparateur de courant précédant le compteur numérique, et la seconde, intègre le courant sur un condensateur pour avoir la valeur de la charge totale à chaque GTU. Au-dessus d'un certain seuil cette charge est stockée dans une mémoire analogique de 32 cellules

Figure 2: Voie anode.

avant que le condensateur ne soit vidé par un interrupteur analogique à la fin du GTU.

Les études ont porté essentiellement sur les points suivants :

- la linéarité et la dynamique des réponses des voies dynode et anode ;

- la rapidité des signaux (résolution en double impulsion < 10 ns) ;

- la compensation des courants de fuite (amplificateur « auto-zéro ») ;

- le fonctionnement des discriminateurs à bas seuil ;

- la stabilité dans le temps de la charge stockée dans les mémoires analogiques.

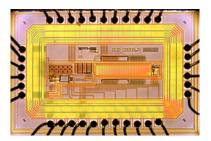

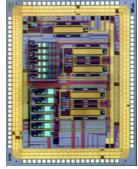

Les résultats des mesures sur les deux premiers prototypes (Figures 3 et 4) sont très prometteurs. Si le 3<sup>e</sup> prototype plus proche de l'architecture finale donne satisfaction, l'étape ultime consistera à réaliser un circuit commun avec nos collègues du Laboratoire INFN de

Figure 3:  $1^{er}$  prototype [voie dynode / surface  $\sim 3$ mm<sup>2</sup>].

Gênes. Ceux-ci ont déjà développé un circuit de traitement des signaux des Photomultiplicateurs à forte dominante numérique (Digital Front-End Electronics).

Ce circuit baptisé **MARS** (Multi Anode Readout System) intégrera à la fois les fonctionnalités numériques et analogiques. Il comprendra 144 voies et sera associé aux 4 Photo Multiplicateurs [4 x 36 anodes et 4 dynodes] d'une même « MicroCellule ».

Figure 4: 2<sup>e</sup> prototype [1 voie dynode & 12 voies anode / surface ~ 12mm<sup>2</sup>].

# Activités de test de circuits intégrés analogiques

Le système robotisé qui a été conçu pour le test de circuits intégrés spécifiques d'ATLAS a donné entière satisfaction. Les premiers types de circuit testés ont été les filtres analogiques (shaper), pour un volume total de 70 000 exemplaires en boîtier QFP100. Ensuite les mémoires analogiques (SCA) ont été testées pour un volume de 80 000 circuits.

Depuis février 2004 une nouvelle série de 30 000 circuits amplificateurs opérationnels de faible offset est en cours de test ; ils sont en boîtier QFP44.

Rappelons qu'un système de marquage à jet d'encre avait été aussi conçu et couplé avec le robot de test. Chacun des circuits testés comporte donc un numéro de série spécifique qui est aussi archivé avec les résultats de test pour la traçabilité.

Cette étape d'identification sera mise à profit dans les prochains mois pour certains circuits numériques, avant leur phase de test, prévue plus tard sur des instruments plus spéciali-

sés; le multiplexeur (SMUX) des liens optiques suivra cette voie tout comme le circuit CALOGIC du LAPP.

Suite aux phases de test et/ou de marquage, nous nous sommes aussi équipés pour conditionner les circuits dans des sachets hermétiques, sous vide ou avec de l'azote.

En plus de tous ces circuits qui entrent dans le cadre d'ATLAS, des demandes ont été exprimées par d'autres expériences de physique comme ALICE. Des contacts sont en cours aussi avec le centre C4I et la société ST Microelectronics.

## **Expérience MUNU**

Après le suivi de l'expérience MUNU à la centrale nucléaire du Bugey concernant l'électronique et l'acquisition du détecteur, le démantèlement de l'expérience a été effectué en 2003. Cela a découlé d'études poussées sur la propreté radiologique pour l'évacuation du matériel en local « propre » situé en zone contrôlée. Le service a dû garantir la propreté radiologique du matériel au travers de la centrale et lors de sa sortie, sa traçabilité, ainsi que l'exécution des procédures données au sous-traitant. Cela a eu pour résultat l'évacuation hors de la centrale et la réintégration dans le milieu civil d'un certain nombre de composantes électroniques du détecteur neutrino vers les différents laboratoires de la collaboration MUNU (châssis NIM, tiroir d'instrumentation, Flash ADC, Photomultiplicateur, etc.).

#### **Activité sur Peren**

Le service électronique a étudié le système de régulation thermique d'un four 3 zones pour le laboratoire de chimie. Ce four « puits » sera utilisé pour le moulage des sels de fluorures, dans les activités du groupe réacteur concernant le projet Peren.

Notre four de 750 mm sera régulé par un superviseur et trois régulateurs esclaves afin d'agir sur trois zones de chauffes indépendantes.

## Microélectronique

# Études, prospectives et recherches

Les nouvelles technologies de microélectronique créent des contraintes de plus en plus sévères pour la conception des circuits intégrés analogiques. Ces cellules analogiques constituent pourtant les premiers étages des systèmes électroniques utilisés pour les expériences de physique. De nombreuses études sont donc menées dans notre laboratoire en tenant compte des critères de basse tension d'alimentation et de faible consommation. Certaines ont déjà trouvé des applications concrètes pour une expérience de physique (comme EUSO), et d'autres ont obtenu le soutien financier de la région Rhône-Alpes à travers le projet MIRA.

Nous donnons ci-dessous des exemples d'études réalisées.

#### A) Convoyeur de courant

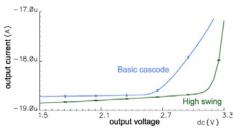

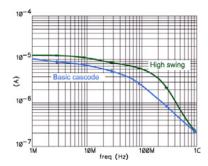

Une structure de préamplificateur convoyeur de courant de type CCII a été finalisée. Elle permet d'améliorer très sensiblement la dynamique et la bande passante, en comparaison avec les architectures cascode classiques, sans augmenter la consommation (Figures 5 et 6)

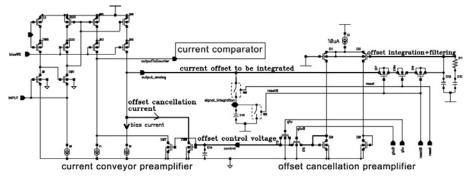

En plus de ces améliorations qui ont été décisives pour l'électronique analogique d'EUSO, une structure auto zéro a été aussi étudiée pour réduire d'un facteur 10 le courant d'offset de ce type de préamplificateur, le ramenant en dessous de 100 nA dans les pires cas.

Le schéma block simplifié de l'ensemble du préamplificateur est donné en figure 7. Il inclut également un étage d'adaptation d'impédance qui est très important contre l'effet de la capacité du détecteur et des capacités parasites.

Figure 5 : Amélioration de la dynamique des miroirs de courant.

Figure 6 : Amélioration de la bande passante.

Figure 7 : Schéma block du préamplificateur de courant utilisé pour les anodes des PM dans EUSO.

#### B) Les comparateurs de courants

Les comparateurs sont souvent utilisés après les préamplificateurs pour délivrer une impulsion de trigger en fonction d'un seuil donné. Pour optimiser la consommation, les comparateurs de courant sont un choix approprié pour être associés avec les préamplificateurs de courant. Trois architectures de ces comparateurs ont été étudiées et testées. Certains peuvent atteindre une résolution de 1  $\mu$ A, pour une consommation qui reste inférieure aux architectures usuelles de comparateurs de tension.

#### C) ADC de type pipe-line

L'objectif visé est un ADC de 10 bits à 2 mW/MS/s. Une bonne maîtrise de cette architecture d'ADC trouvera de nombreuses applications dans l'électronique « front-end » de plusieurs expériences futures de physique. Les technologies microélectroniques actuelles, peu favorables à l'analogique, imposent que les signaux dans la chaîne électronique soient numérisés au plus tôt. Un savoir faire dans les ADC permettra de concevoir des circuits dont les caractéristiques seront réellement adaptées à l'application visée. Il est aussi très important dans le cadre de la valorisation. Cette étude a été sélectionnée par la région Rhône-Alpes qui lui a accordé un financement dans le cadre MIRA en 2003.

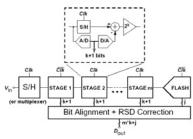

L'architecture étudiée actuellement est la structure dite « pipe-line » dont le bloc fonctionnel est représenté figure 8.

Figure 8 : Architecture fonctionnelle d'un ADC de type pipe-line.

Ce type d'ADC intègre de fait des cellules de mémoires analogiques ou Sample/Hold (S/H) et des ADC de faible résolution. métages presque identiques sont en cascade, délivrant chacun k+1 bits  $(0,5 \le k \le 1,5)$ . Le signal de départ à numériser est échantillonné et grossièrement numérisé sur k+1 bits, ensuite le résultat numérique est reconverti en analogique avant d'être soustrait du signal de départ. Le résidu ainsi généré est amplifié avant de passer ensuite à l'étage suivant. Un intérêt de cette structure est la possibilité de faire du traitement parallèle, car une fois qu'un étage a fini de numériser le signal venant d'un détecteur, il redevient disponible pour traiter le signal suivant venant d'un autre détecteur : c'est le concept « pipeline ».

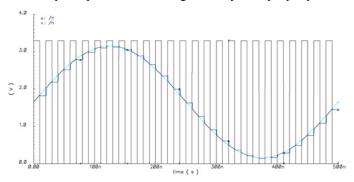

Plusieurs cellules importantes ont été étudiées dans le cadre de ce projet d'ADC. Nous présentons deux exemples typiques : les switch à grande dynamique figure 9, et les échantillonneurs/bloqueurs rapides de faible consommation.

L'objectif est de pouvoir échantillonner des signaux dont l'amplitude est proche des niveaux d'alimentation du circuit.

Cette architecture de switch simulé dans une configuration R-C d'échantillonnage donne le résultat suivant qui montre qu'on peut couvrir une gamme dynamique jusqu'à

Figure 9 : Switch CMOS à dynamique élargie.

Figure 10 : Simulations à 100 MHz d'un switch à dynamique élargie alimenté sous 3,3 V.

#### VDD - 0,2 V (Figure 10).

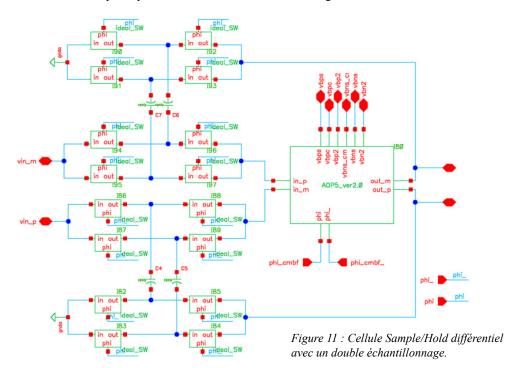

Pour l'étage d'entrée de l'ADC nous avons étudié une cellule S/H différentielle et à double échantillonnage autour d'un amplificateur dont le produit gain \* bande est de 300 MHz avec une consommation totale de 600  $\mu$ W.

Le schéma de principe de cette cellule est montré à la figure 11.

#### D) Générateur d'un signal sinusoïdal pour le projet MACHe3

Cette étude rentre dans le cadre de la conception d'un circuit intégré de détection synchrone. Un générateur numérique d'une fonction sinusoïdale codée sur 9 bits a été conçu. Ce signal est ensuite converti à travers un DAC pour donner un signal analogique. Après un filtrage du premier ordre, les simulations montrent un spectre très propre avec un rapport entre le fondamental et le premier harmonique de 3 000. La fréquence du signal peut aller de 1 à 10 kHz. Dans le cadre du projet MACHe3, ce signal définira la fréquence de référence pour la détection synchrone.