## **Acquisition de Données**

G. Barbier, O. Bourrion, J. Bouvier, B. Boyer, F. Pancher

This service is specialised in the real time acquisition of data and the control of experiments. It took a part in the majority of the experiments in which the LPSC is involved. A large amount of work has been dedicated to the hardware and software development for the control of the coolers for the Planck experiment. Development has also continued on the phase two of the electronic for  $G\theta$  experiment.

#### Introduction

Au cours de ces deux dernières années, le service a participé à la plupart des expériences dans lesquelles le LPSC est impliqué. Si les expériences AMS, GRAAL et Structure Nucléaire ont fonctionné sans modifications majeures et ne nous ont demandé que des interventions ponctuelles, d'autres expériences telles que ATLAS, Planck, GØ, Physique des Réacteurs et récemment EUSO, ont nécessité des développements matériels et logiciels plus importants. Le service a consacré également une partie de son temps en recherche et développement pour réaliser un module VME (TEMPO) de gestion d'acquisition.

# Expérience ATLAS : Tests TBF (très basse fréquence)

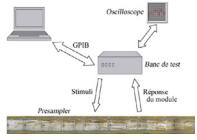

Figure 1

Ce dispositif sert à vérifier que le module prééchantilloneur n'a pas été détérioré suite aux manipulations mécaniques dues à son insertion dans la roue du calorimètre.

Pour faire ces tests un PC communique à travers un lien GPIB via un banc de test avec un oscilloscope. Celui-ci récupère les informations électroniques émises par le prééchantillonneur en réponse des stimuli émis par le banc de test.

Pour valider le module, on procède par comparaison avec la mesure faite en sortie de fabrication.

## Expérience Planck

Le service est chargé de l'étude et de la réalisation de l'électronique logique et de l'informatique nécessaires au pilotage de la machine cryogénique à 20 K « Sorption Cooler » développée par la NASA au Jet Propulsion Laboratory et de l'électronique de la machine à dilution 100 mK développée par la société Air Liquide.

## Électronique logique et informatique de commande du 20 K

Le premier prototype Elegant Bread Board Model (EBB) a été développé et testé dans les locaux du LPSC tant au niveau logiciel que matériel. Il a été ensuite connecté à la machine cryogénique du Jet Propulsion Laboratory de la NASA courant 2002. Ces premiers résultats ont été concluants et ont démontré que l'électronique et le logiciel DSP pilotent et communiquent avec la machine cryogénique selon les spécifications.

Suite à des changements majeurs du cahier des charges proposés par le JPL, le logiciel

#### Services techniques & administratifs

prototype EBB a été en grande partie réécrit et a donc du être testé à nouveau au JPL début 2003

Depuis, le service a réalisé le développement du modèle CQM (Cryogenic qualification model), modèle intermédiaire entre le prototype EBB et le modèle de vol. A partir de notre design, la fabrication de ce modèle est assurée par une société agréée par les instances spatiales. Les critères de fabrication suivent les normes spatiales alors que les composants implantés sont des composants standards. Le logiciel a également été modifié pour s'adapter aux normes spatiales et pour implémenter le dialogue avec le satellite imposé par le constructeur.

Ce nouveau modèle devrait être testé au LPSC début 2004 et la connexion avec l'appareil cryogénique devrait s'effectuer au cours de l'été.

## Électronique logique de commande du 100 mK

Le premier prototype Elegant Bread Board Model (EBB) de la carte électronique a été réalisé. Le service a été chargé de la partie logique de cette carte, de l'interfaçage et du dialogue avec l'unité processeur via un bus RS422. Cette carte devrait être testée au début de l'année 2004 avec le simulateur de la machine 100 mK puis sur le prototype de la machine cryogénique au sein de la société Air Liquide.

#### Carte de simulation de la machine 100 mK

Cette carte permet de simuler le comportement de la machine à froid contrôlée par l'électronique DCE ainsi que ses divers capteurs associés.

Cette carte permet de simuler :

- le comportement électrique des 12 vannes (6 vannes d'injection, 4 vannes haute pression, 2 vannes d'échappement, ainsi que le signal de retour généré par celles-ci. Les vannes sont bistables et à double commande, certaines fournissent un signal de retour qui est fonction de leur position,

- Figure 2 : Photo de la carte câblée.

- le comportement électrique des 6 capteurs de pression (2 capteurs haute pression, 4 capteurs basse pression);

- le comportement électrique des 14 capteurs de température (6 capteurs de type PT100, 8 capteurs de type Cernox);

- le comportement électrique des 14 capteurs de température. Ce sont simplement des résistances permettant une dissipation de puissance adéquate (2 heaters de 2 W, 2 heaters de 150 mW, 2 heaters de 25 mW et 2 heaters de 200 mW).

## Expérience GØ

#### Carte CEDFPD

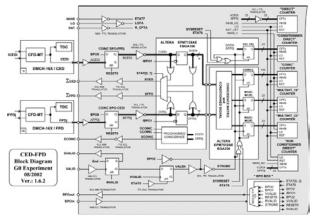

Pour la partie mesure aux angles arrières de l'expérience GØ, il a été développé une carte au format VXI (taille C) pour l'acquisition de 2 octants, le détecteur étant subdivisé en 8 octants. Celle-ci est chargée de compter, pour un octant, les coïncidences valides de signaux issues de 9 détecteurs proches du Cryostat (appelés Cryostat Exit Detectors) et de 14 détecteurs situés à environ 2 mètres de la cible (appelés Focal Plan Detectors), ceci dans une fenêtre en temps de 8 ns sur un temps de cycle de 32 ns.

La validation de ces coïncidences est faite par un détecteur Čerenkov.

Outre ces coïncidences il est aussi compté un certain nombre de signaux issus de com-

#### Services techniques & administratifs

Figure 3 : Synoptique carte CEDFPD.

binaison des signaux d'entrée, de la fenêtre en temps et de l'information Čerenkov, tout ceci portant à 241 le nombre de voies de comptage par octant soit un total de 482 compteurs pour la carte.

La partie comptage est effectuée à l'aide des circuits ASIC COUNT32 (32 compteurs 32 bits) développés au LPSC. La partie coïncidences et détermination de validation

Figure 4

est réalisée à l'aide d'un circuit de logique programmable (FPGA) encapsulé dans des boîtiers BGA et FBGA.

#### Module de test pour la carte CEDFPD

Ce module permet de tester et de caractériser la carte de coïncidences CEDFPD utilisée pour les angles arrières lors de l'expérience GØ. Il doit fournir des stimuli conformes en temps, fréquence et forme par rapport aux signaux que la physique générera. Il permet aussi de tester et d'analyser les signaux sortant de la carte CEDFPD afin de déterminer s'ils sont conformes au cahier des charges. Nous devons pouvoir gérer les normes VXI et VME. Un circuit programmable de la famille FPGA (marque XILINX) assure les fonctions essentielles de la carte.

Figure 5

## **▶** Physique des réacteurs : carte RH\_flash

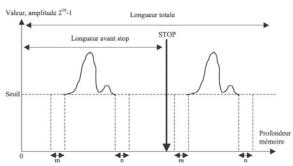

Figure 6

Pour permettre d'avoir une bonne résolution temporelle lors de l'échantillonnage des signaux de détecteur, un module d'acquisition 4 voies basé sur des codeurs flash 100 MHz a été développé (Figure 6). Il a pour fonction de convertir et de stocker dans une mémoire de sortie l'image des données analogiques présentées à l'entrée, et ce, dans une fenêtre temporelle donnée située autour d'un signal de stop (un peu comme un oscilloscope numérique), voir figure 7. Il est conçu au format VME avec connecteur auxiliaire, il a une largeur d'une unité.

Ce module permet une grande fréquence d'échantillonnage couplée à une fréquence d'acquisition élevée (grâce aux codeurs flash). Pour ce faire, la carte mémorise uniquement les données jugées « utiles » (dépassant un certain seuil), ce qui peut par exemple être utile pour voir des pics dans un spectre et les situer les uns par rapport aux autres.

À partir d'un seuil prédéfini, tout pic dépassant ce seuil sera réellement stocké en mémoire et finalement visible par le bus VME. La position et les valeurs du pic lui-même seront stockées, ainsi que les m valeurs précédentes et les n valeurs suivantes. Évidemment, si le seuil est 0, cela revient à désactiver le système de traitement et toutes les données seront stockées.

Figure 7

#### **Explication fonctionnelle**

Grâce à des offsets programmables chaque entrée peut accepter différents types de signaux en fonction des besoins expérimentaux. La fréquence d'échantillonnage est programmable jusqu'à 100 MHz.

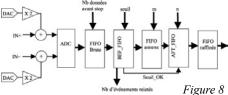

La première FIFO (Figure 8) pouvant contenir 32 K échantillons sert à stocker les données brutes en provenance du flash ADC. Son fonctionnement continu en buffer circulaire permet de garder en mémoire les données avant le trigger.

Le module de traitement BEF\_FIFO sert à relire les données brutes et à marquer toutes les données dépassant le seuil programmé avant de les stocker dans la mémoire FIFO annexe. Elle fonctionne aussi en buffer circulaire et est programmée avec la valeur m, permettant de stocker les données avant pic dans le module de traitement AFT\_FIFO. Ce module est ainsi informé de l'entrée prochaine dans le pic et active le stockage en FIFO\_raffinée. Le module BEF\_FIFO contient un compteur d'événements rejetés, qui est incrémenté à chaque signal stop alors qu'un traitement est déjà en cours.

Le module de traitement AFT\_FIFO a aussi d'autres rôles, ainsi lorsque l'arrivée imminente d'un pic est détectée, ce module insère une marque relative de pic, c'est-à-dire qu'il indique le nombre de cycles écoulés depuis le début de la fenêtre. Il ajoute une marque de fin de fenêtre à la fin des données.

Au final, les données stockées dans la FIFO\_raffinée ne sont que celles supérieures au seuil plus m données avant et n données après. Dans le cas d'une fenêtre sans pic, il n'y aura qu'une marque de fin de fenêtre dans le buffer de sortie.

Tous les paramètres de ce modules sont programmables par l'intermédiaire du bus VME à l'exception de l'horloge utilisée pour cadencer l'échantillonnage qui est générée sur la carte et configurable par roue codeuse.

## **Acquisition**

Un nouvel ensemble d'acquisition a été développé pour les expériences sur GENEPI II. L'électronique est située dans un châssis VME couplé à une station de travail via une carte processeur et un lien ethernet. Le timing de l'acquisition est géré par le module Tempo et les informations expérimentales peuvent entrer sur des codeurs flash RH\_flash sur des codeurs d'amplitude ADCVME8V et sur des échelles de comptage. La configuration de l'expérience ainsi que la programmation des différents modules sont réalisées graphiquement grâce à un programme développé avec XFORM. L'acquisition est une adaptation du logiciel OASIS développé par le laboratoire de l'IPN Orsay.

## ▶ Recherche et développement : module tempo

Le module **tempo** a pour fonction de générer les différentes impulsions nécessaires au séquencement d'une acquisition. Il est au standard VME et de largeur une unité.

Par rapport à un signal d'entrée, ce module permet la génération de 4 impulsions de retards et largeurs variables tout en gérant le temps mort. Il a aussi des fonctionnalités permettant :

- le comptage du nombre total d'événements ;

- le comptage des événements rejetés :

- la génération d'une interruption après chaque événement accepté (délai programmable) ;

- la possibilité de stopper une acquisition sur un temps écoulé ou sur un nombre d'événements donné avec possibilité de génération d'une interruption.

Tous les signaux entrées et sorties sont au format NIM et toutes les fonctionnalités du module sont programmables pour être adaptées à chaque type d'expérience. Pour faciliter la mise au point d'une acquisition, un générateur manuel d'événement est inclus sur la carte.

#### **Explication fonctionnelle**

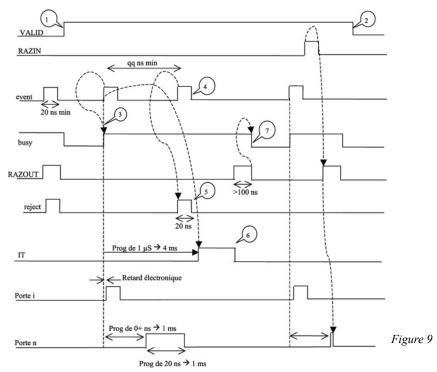

- [1], [2] : La carte est activée par une écriture VME, alors VALID passe à l'état actif et la carte sort du temps mort. Si elle est désactivée, la carte arrête de générer des portes ;

- [3] : Un événement est accepté uniquement si la carte n'est pas en temps mort ;

- [4], [5]: Si un événement arrive alors que la carte est en temps mort un signal **reject** est généré, il n'y a pas de contrainte de rapidité entre la réception de **EVENT** et la génération de **reject**;

- [6]: Le fait de recevoir un **EVENT** valide génère une interruption après un délai programmable;

- [3], [7]: La carte entre en **busy** lorsqu'un **EVENT** valable est reçu, et en ressort dès que le signal **RAZout** est relâché. L'entrée en temps mort doit être la plus rapide possible;

- Le signal RAZout est généré soit si une écriture VME dans le registre approprié a eu lieu et si les gates sont terminées, soit par un RAZin valide (c'est-à-dire pas entre IT et écriture VME) et dans ce cas, il doit arrêter toutes les portes potentiellement encore en route, et arrêter la génération d'IT;

- Le signal **RAZout** peut être rallongé si nécessaire. Ainsi lorsque un **RAZin** arrive, on rallonge le **RAZout** pour permettre la décharge des capas. Dans le cas où il arrive après, on rallonge uniquement si nécessaire (à savoir si les décharges ne peuvent s'imbriquer).

## Slow control sur les accélérateurs GENEPI

Le service participe à la maintenance et au suivi des systèmes de commande à distance des accélérateurs implantés à Cadarache et au LPSC. Cela met en œuvre toute une batterie de PC104 associée à un logiciel de commande développé au laboratoire.

## **Euso**

Le service a été impliqué dans la conception du 3<sup>e</sup> prototype de l'ASIC AFEE développé par le LPSC. Sa contribution a été la conception, la synthèse et le routage des fonctionnalités numériques permettant la gestion des mémoires analogiques. Dans un deuxième temps, l'assistance du service a été nécessaire pour développer la partie acquisition du dispositif de test du proto ASIC.